OVERVIEW

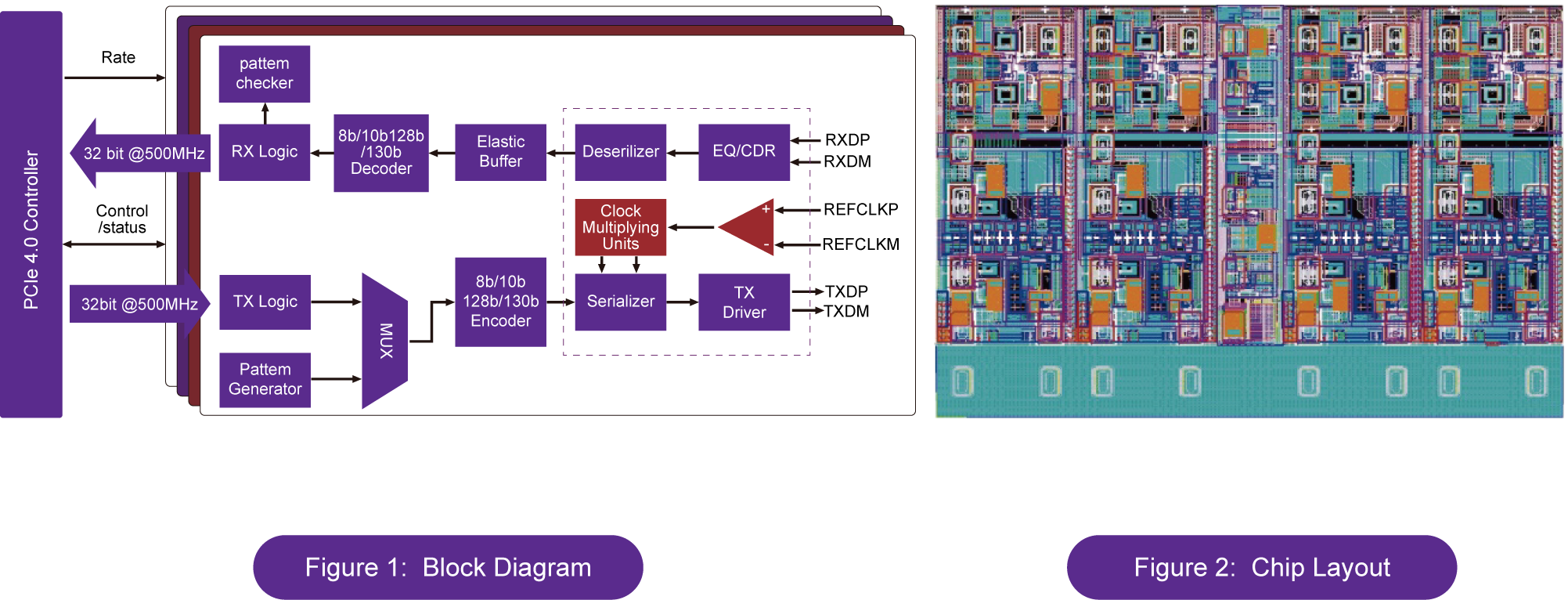

MSquare's PCI Express 4.0 PHY IP includes a high-speed, highly-efficient, and cost-effective transceiver to turbocharge today's high-performance and high-bandwidth applications such as data centers, automotive, enterprise computing, and high-performance embedded systems.

The PCIe IP boasts a low power consumption and compact silicon footprint. Its robust PHY architecture tolerates process, voltage, and temperature (PVT) variations. This IP integrates high-speed mixed-signal circuits to support PCIe 4.0 traffic at 16Gbps. It is backward compatible with PCIe 3.1 data rates at 8.0Gbps, PCIe 2.1 at 5.0Gbps, and PCIe 1.1 at 2.5Gbps. The multi-tab transceiver design, accompanied by a robust BIST, an embedded bit error rate (BER) tester, and an internal eye monitor, enables designers to control, test, and monitor signal integrity without the need for expensive test equipment.

HIGHLIGHTS

Compiles with PCIe 4.0, 3.1, 2.1, 1.1 and PIPE 4.4.1 specifications

Supports all power-saving modes (P0, P0s, P1, P2) as defined in PIPE 4.4.1 specifications

Supports L1 PM/CPM substates with CLKREQ#

Supports the separate REFCLK Independent SSC (SRIS) architecture

Accessible register control TX PLL bandwidth, TX de-emphasis level, CDR bandwidth, and EQ strength

Supports both FOM and DIR modes for Link-EQ Training

Supports robust BIST/DFT functions for mass production tests

Supports bifurcation with 4-lane x 1 or 2-lane x 2 configurations