OVERVIEW

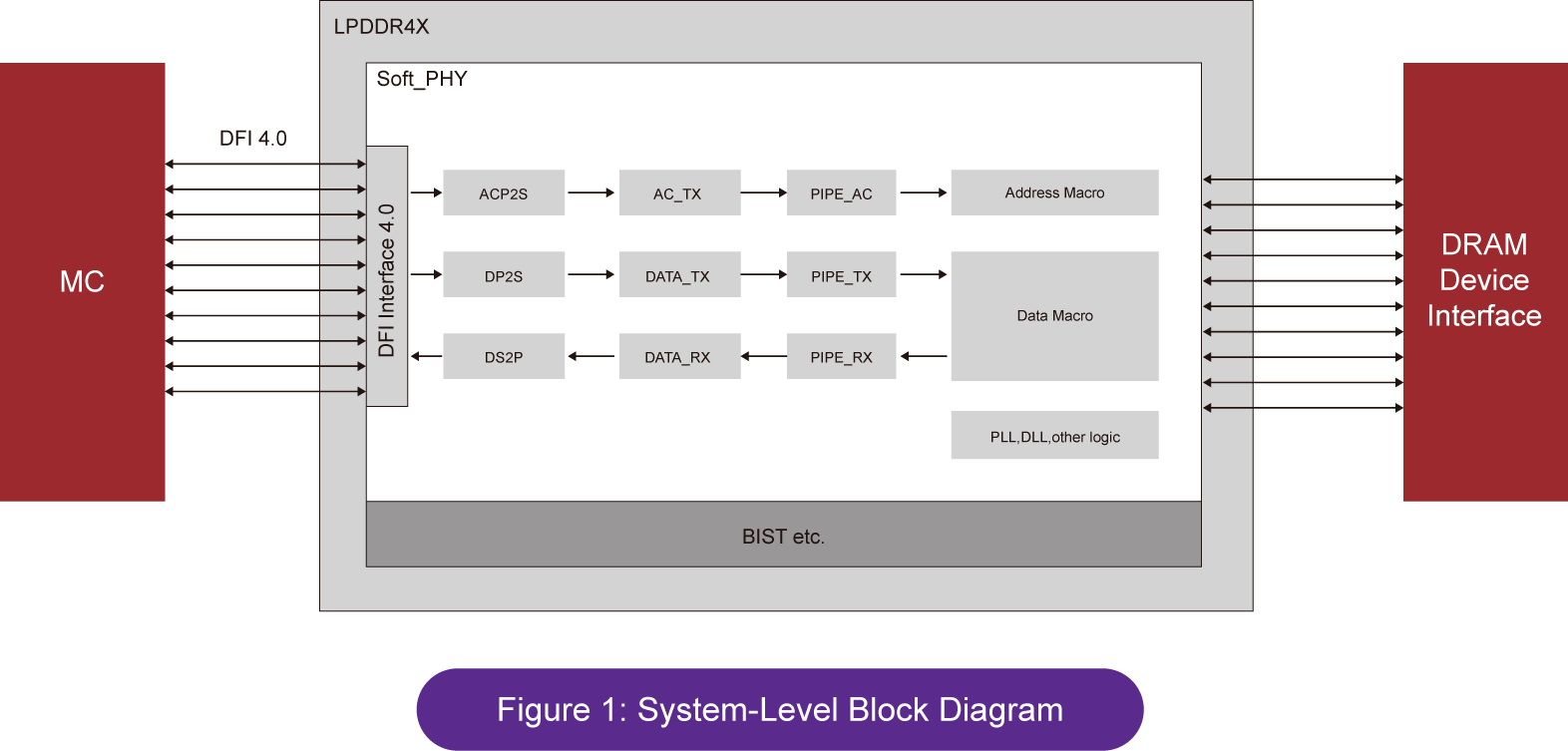

MSquare's LPDDR4X PHY is a transceiver physical layer IP interface solution designed for ASICs and SOCs. Compatible with the universal IP protocol DFI 4.0, it operates at a data rate of up to 4267Mbps with a 16-bit data width per channel. As depicted in Figure 1, the LPDDR4X PHY block diagram for system application includes a data and address transmit path, a receiver data path, a PLL block, and more. Featuring a hybrid analog/digital architecture, MSquare's IP delivers low power consumption, a compact footprint, and robust performance, making it well-suited for LPDDR4X applications.

HIGHLIGHTS

Compatible with LPDDR4X, with a maximum rate up to 4267Mbps

Compliant with DFI 4.0 for PHY and control interfaces

Flexible channel architecture

Supports PHY-independent training mode using an embedded processor

Supports dual rank

DFS supports 4 trained frequencies

Supports BIST and loopback modes

Supports background tracking for PVT compensation

Integrated low-jitter PLL and DLL

Compliant with JEDEC standard JESD209-4C