2024年1月25日,海力士公司發佈了2023年度財報。 值得注意的是,在該財報中,HBM3的營收較2022年增長了5倍。 公司高層表示端側AI市場將在2025年及以後迎來重大發展。 此外,海力士公司將持續推進用於人工智慧的記憶體晶片HBM3E的量產,並推動HBM4的研發。 這一系列發言無疑引發了業界從業人員對HBM未來市場的更多期待。

HBM(High Bandwidth Memory),即高頻寬記憶體,按照JEDEC的分類屬於圖形DDR。 在科普視頻的第四講《風頭正夯的HBM》中,我們對HBM的3D堆疊結構、各代HBM的速率和容量等參數進行了簡要介紹。 通過採用矽穿孔技術(Through Silicon Via,簡稱“TSV”),HBM實現了晶片的垂直堆疊,類似於將數個DRAM裸片像樓層一樣疊加,以提高輸送量並克服單一封裝內頻寬的限制。

這項創新設計,通過TSV科技的應用,成功地解决了當前DRAM領域所面臨的兩個核心問題:一是明顯提升了可用頻寬,從而使資料傳輸效率得到顯著提高; 二是有效地降低了功耗,使得HBM在性能和效能方面都取得了顯著的突破。 事實上,HBM被認為是當下功耗效率最高的DRAM產品,其高頻寬和高延遲特性使其成為高端GPU顯存的理想選擇。

HBM在應對高端GPU顯存的需求時,展現出其卓越的效能。 其特有的高頻寬和相對較高的延遲特性使其非常適用於對頻寬需求較高、對延遲不太敏感的負載。 在服務器領域,一種常見的應用方案是將HBM與DDR搭配使用,其中HBM負責處理高頻寬小容量的數據,而DDR則處理稍低頻寬但大容量的數據。 這種巧妙的組合進一步優化了系統的整體效能和能效。

HBM主要應用領域

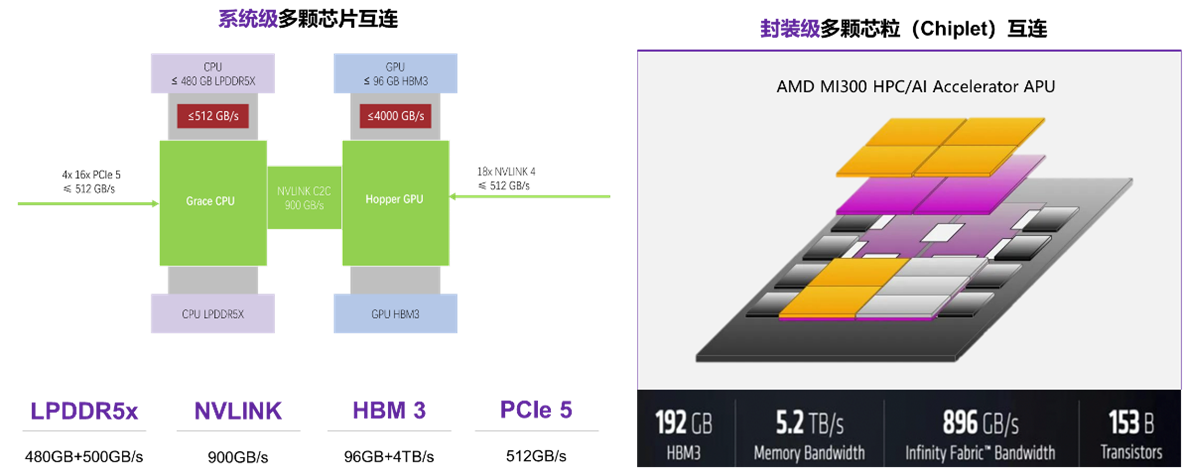

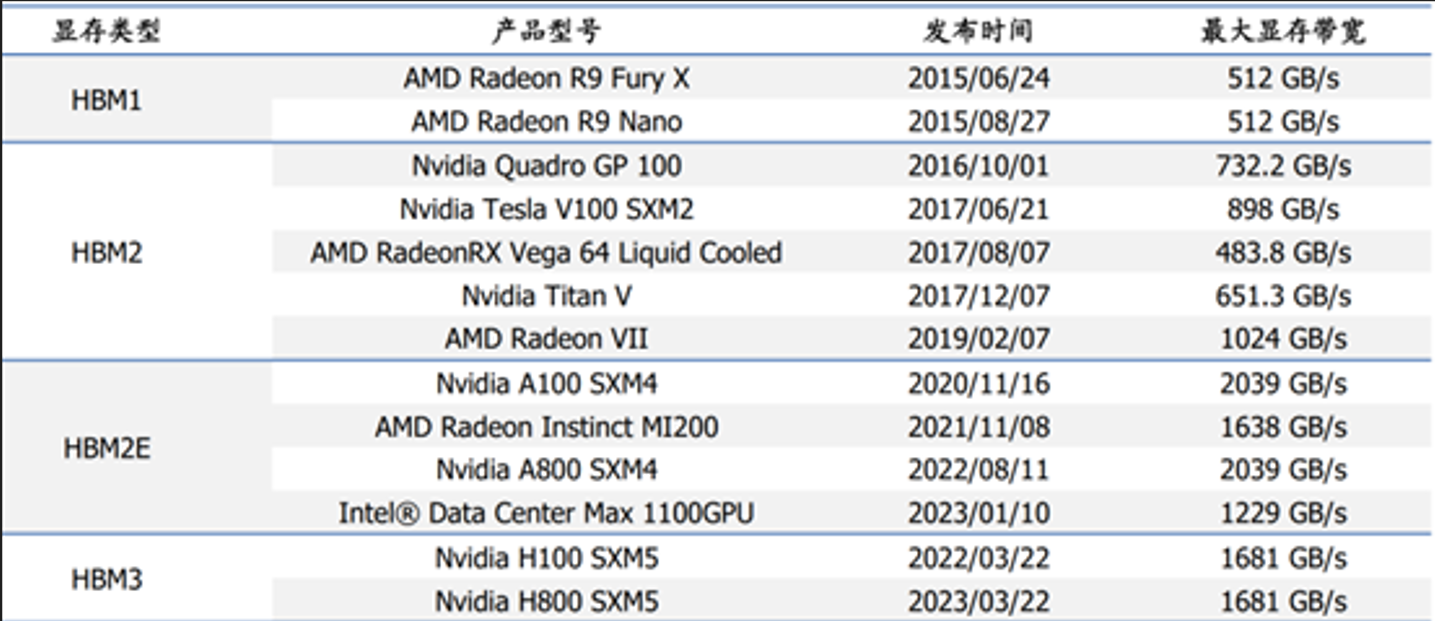

HBM廣泛應用於高頻寬和高容量的場景,並已成為主流AI訓練晶片的常用選擇。NVIDIA和AMD等領先廠商率先採用了HBM顯存科技,其中NVIDIA的H系列產品是最早搭載HBM3的GPU產品,能够顯著提升AI大模型的訓練速度。

NVIDIA的H100是專為大型語言模型設計的產品,通過PCIe橋接設備,兩張H100計算卡可以組成一個系統。 單個H100支持高達40Tb/s的IO頻寬,總共提供188GB的HBM3顯存。 在一個服務器中,基於四對H100和雙N VLINK的配置,可以將大型模型的計算處理速度提升至少10倍。 通過軟硬體的優化,訓練速度最高可提升30倍。

在HBM作為AI服務器最優選記憶體的大背景下,是否會替代傳統DDR成為電腦記憶體的主流,仍然存在一些問題。 從HBM的形態可以看出,它雖然在高頻寬、高容量的場景中表現卓越,仍然存在一些缺點。 首先,HBM在靈活性方面表現欠佳。 由於HBM與主晶片封裝在一起,缺乏容量擴展的可能性。 其規格在出廠時已被固定,無法靈活調整。 其次,相較於DDR,HBM的記憶體容量受到更大的限制。 現時主流AI/GPU晶片採用的是HBM3產品,單個HBM Stack僅能提供16GB容量,即使一顆晶片搭載了6個HBM Stack,總容量也只有96GB。 與DDR相比,這樣的容量仍然相對較小。 第三,HBM相對於DDR而言,存在較高的訪問延遲。 這一特性在某些應用場景下可能成為一個不可忽視的瓶頸,影響數據的快速訪問。

短期來看:

HBM很難在電腦(PC)領域替代DDR記憶體。 在PC應用中,對各種隨機存儲訪問的需求很高,而對延遲的敏感度天生更强。 事實上,PC應用對低延遲的要求甚至高於對高頻寬的要求。 在消費市場上,常見的普通PC需要靈活地堆疊32GB以上的記憶體,而考慮到高端服務器通常具有96個DIMM插槽,最多可以擴展到12TB的容量。 此外,還有一個非常重要的因素,即HBM的成本相對於DDR而言過高,HBM的昂貴價格成為其在個人電腦領域推廣的一大障礙。

長期來看:

HBM在AR/VR設備、汽車自動駕駛等領域將會迎來更廣泛的應用。 在AR/VR設備方面,以HTC VIVE Pro2為例,GTX1060即可滿足當前需求,並不迫切需要HBM等高頻寬產品,未來隨著顯示需求的新增,高頻寬產品的需求可能逐步增加。 在汽車領域,當前的自動駕駛系統並不急需HBM的高頻寬。 例如,英偉達的Jetson AGX Orin採用256比特的LPDDR5,其頻寬最高為204.8GB/s。 然而,長期來看,隨著L3/L4等級別自動駕駛汽車逐漸實現,對HBM的需求也將提升。 以L3級別自動駕駛為例,其頻寬要求通常在600GB/s至1TB/s之間,單車可使用2個HBM2e或者1個HBM3; 而對於L4級別自動駕駛,其頻寬需求一般在1TB/s至1.5TB/s之間,單車可使用3個HBM2e或者2個HBM3。

作為UCIE產業聯盟的成員,奎芯科技皆在推動芯粒互聯科技的發展和應用。 在高速介面IP領域,奎芯科技擁有深厚的科技積累和豐富的產品系列。 基於這些高端的高速介面IP,奎芯科技提出了一種名為M2LINK的計算機系統互聯架構方案。

M2LINK包含三種Chiplet方案:C2IO,與串列匯流排介面相聯; C2M,與記憶體匯流排相連; 以及C2C,實現計算Die之間的互聯。 奎芯科技將不斷努力以滿足Chiplet領域晶片設計企業的需求,並致力於打造一個開放生態的Chiplet服務平臺,為集成晶片和芯粒行業的創新和發展提供全方位的支持。