2024年的GPU科技領域的動態看起來非常激動人心! 輝達、英特爾以及Meta都在不同的方面推出了令人印象深刻的新產品和科技。

輝達的Blackwell B200:這是一款巨大的GPU,內部集成了2080億個電晶體,尺寸是其前一代的兩倍; 採用了定制的兩掩模版極限N4P TSMC工藝進行製造,通過10TBps的晶片到晶片連結連接成為單個GPU; 採用了Chiplet科技,在單個封裝上配備了兩個GPU晶片,並通過高頻寬I/O連結連接; 提供192GB的HBM3E記憶體,記憶體總頻寬為8TB/s。

英特爾的Gaudi 3加速器:這是英特爾子公司Habana Labs的下一代高性能人工智慧加速器。 集成了HBM2e記憶體控制器,每個晶片提供128GB的記憶體,總記憶體頻寬為3.7TB/s。 採用了Chiplet設計,每個晶片配備了兩個計算Die,轉向了具有兩個計算集羣的Chiplet的設計。

Meta的下一代訓練和推理加速器:集成了LPDDR5記憶體控制器,單晶片可擴展128GB LPDDR5記憶體,總記憶體頻寬為204.8GB/s; 採用TSMC 5nm的工藝帶來了90W的功耗表現; 該晶片的架構從根本上側重於為服務排名和推薦模型提供計算、記憶體頻寬和記憶體容量的適當平衡。

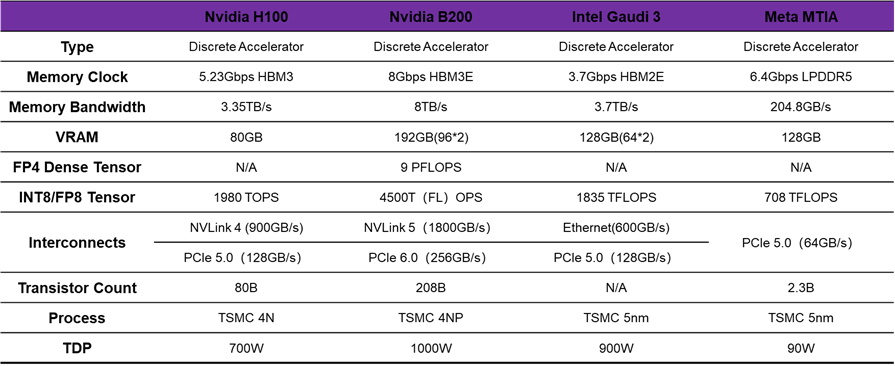

小編根據市場上應用的標杆H100,整理了如圖的硬體參數對照表。

可以看到,2024年GPU科技領域的角逐依舊火熱,各大科技巨頭爭相推出新一代的創新產品和科技。 輝達、英特爾以及Meta在AI算力領域展開了一場激烈的競爭,為了讓我們更好地理解這一場景,讓我們先來梳理一下最新的四大趨勢。

NVIDIA B200 and Intel Gaudi 3

Chiplet科技的崛起

從霄龍二代和銳龍三代開始,AMD就採用CPU Die + IO Die的Chiplet組合管道來擴展CPU算力,自此Chiplet科技被廣泛的傳播開來。 本次發佈的NVIDIA B200在單個封裝上配備兩個GPU晶片,據NVIDIA稱,這兩個晶片作為“一個統一的CUDA GPU”運行,可提供完整的效能,其關鍵在於晶片之間的高頻寬I/O連結,NVIDIA將其稱為NV高頻寬介面(NV-HBI:NV-High Bandwidth Interface),並提供10TB/秒的頻寬。 自此,NVIDIA終於在他們的旗艦加速器實現了Chiplet化。 Intel Gaudi 3採用的是台積電5nm工藝,在晶片設計上,Gaudi 3轉向了具有兩個計算集羣的Chiplet的設計,而不是Gaudi 2所採用的單個集群的方案。 這與NVIDIA最近發佈的Blackwell加速器類似,兩個相同的晶片被放置在一個封裝上,並通過高頻寬連結連接,以便為晶片提供統一的記憶體位置空間。 Intel沒有透露連接晶片的晶片到晶片連結的任何重要細節,現實尚不清楚實際上有多少頻寬可用於跨越die。

HBM依舊是AI領域記憶體擴展的主流

NVIDIA B200提供192GB的HBM3E,每個Chiplet與4個HBM3E記憶體堆疊配對,總共8個堆疊,形成8192比特的有效記憶體匯流排寬度。 該晶片的HBM記憶體總頻寬為8TB/秒,每個堆疊的頻寬為1TB/秒,即每個引脚的資料速率為8Gbps。 記憶體總頻寬幾乎是H100記憶體頻寬的2.4倍。

Intel Gaudi 3集成了HBM2e記憶體控制器,與Gaudi 2支持的記憶體類型相同,國內頭部AI企業現有產品基本也是集成HBM2e內容。 由於其堅持使用HBM2e,可用的最高容量堆疊為16GB,為加速器提供了總共128GB的記憶體。 其時鐘頻率為3.7Gbps/pin,總記憶體頻寬為3.7TB/秒。 每個Gaudi 3晶片都提供4個HBM2e PHY,使晶片的記憶體堆疊總數達到8個。

PCIe 6.0的應用

隨著GPU算力的不斷提升,對於資料傳輸速率的需求也日益增長。 Astera Labs展示了PCIe 6.0連接科技,應用於輝達的Blackwell B200,為其提供了更高的資料傳輸速率和更强的擴展性能。 這標誌著PCIe 6.0在GPU平臺上的首次落地,為未來的GPU科技發展奠定了堅實的基礎。

光互連與電互聯的並存

輝達還公佈了由GB200驅動的GB200 NVL72,這是一個多節點、液冷、機架式系統,適用於計算最密集的工作負載。 它結合了36個Grace Blackwell超級晶片,其中包括72個Blackwell GPU和36個Grace CPU,通過第五代NVLink互連。 為了支持下一代AI加速晶片,Meta也開發了一個大型機架式系統,最多可容納72個加速器。 它由三個主機殼組成,每個主機殼包含12個板,每個板包含兩個加速器。

輝達發佈的GB200 NVL72這個架構引發了光互連和銅互連的爭議。 引用資訊平權的總結就是GB200 NVL72通過Chiplet、網絡、近存等等環節升級帶來的系統升級,打造了一個高度濃縮和緊耦合的超節點,且因為壓縮到一個rack,用銅替代了之前256卡互聯的網絡成本,實現了超高性價比。 光互連和電互聯是緊密連繫、互相補充的,所謂的“光進銅退”,可能只是一個美好的願景,兩者會長期共存,負責不同尺度下的訊號互聯。 計算與存儲晶片的高速電信號必須先在package上進行一段距離的傳輸,再通過光學IO互聯到更遠的節點處。 AI的爆發,導致晶片間的互聯需求更加重要。 長遠看,電晶片與光引擎的距離會越來越短,聯系會愈加緊密。

在AI浪潮的推動下,晶片間的互聯需求愈發凸顯其重要性。 輝達發佈的GB200 NVL72以及Meta的下一代加速晶片,均對光互連與電互聯科技進行了深入的探索。 這些科技的實現離不開先進的IP支持。 在這個背景下,奎芯科技在介面IP和Chiplet領域的研發工作顯得尤為關鍵。

奎芯科技作為晶片產業鏈上游的關鍵技術企業,已經在短短的時間內推出了多個自研高速介面IP,如LPDDR5X、HBM、UCIe等,並在知名廠商的工藝節點上得到了驗證和量產。 這些IP和Chiplet產品的成功應用,不僅豐富了資料中心、汽車電子、物聯網和消費類電子等領域的解決方案,更為GPU和AI科技的發展提供了强有力的支持。

展望未來,隨著AI科技的不斷突破和GPU科技的不斷進步,對介面IP和Chiplet的需求將更加旺盛。 奎芯科技將繼續加大在介面IP和Chiplet領域的研發投入,推出更先進的IP產品,以助力AI科技的發展。