在2023年4月,我們分享了一篇關於Chiplet D2D介面技術的文章,重點介紹了Chiplet的歷史以及為何在算力時代選擇Chiplet科技等主題。 文章通過這些話題引出了Chiplet的關鍵技術之一,即D2D互聯科技。 在討論D2D互聯時,我們不可避免地要提到2023年度備受關注的UCIe互聯協定。

作為全球UCIe互聯的主要貢獻者,英特爾在2023年9月的創新大會上展示了一款名為Pike Creek的測試晶片,該晶片由基於UCIe互聯的小晶片構成,綜合了包含英特爾3nm UCIe IP的晶片和包含台積電N3E、Synopsys UCIe IP的晶片,通過英特爾EMIB封裝實現通信。 這款晶片成為全球首款基於不同公司、代工廠以及科技節點設計的UCIe互連晶片,備受矚目。

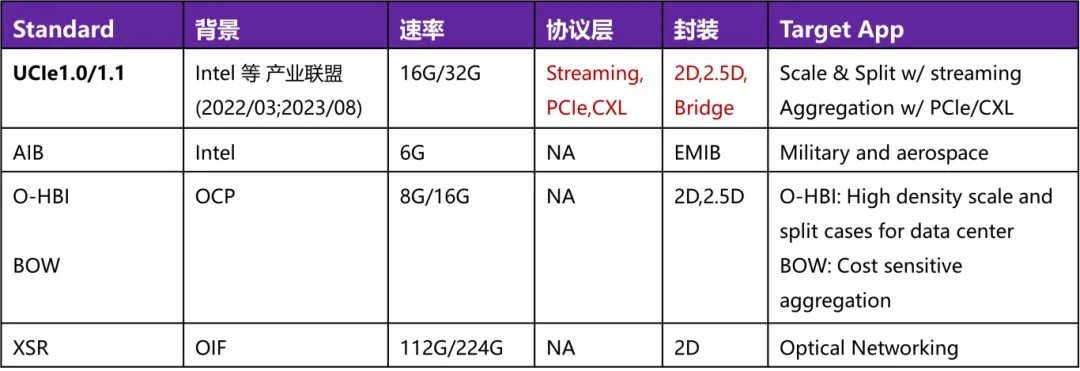

D2D介面協定對比

UCIe並非唯一的D2D介面協定。 在UCIe協定出現之前,全球主要晶片企業,如英特爾、NVIDIA和AMD等,採用私有協定作為D2D互聯協定。 當時,超大型晶片公司並沒有採用其他公司的晶片互聯來擴展晶片能力的需求場景。 直到英特爾基於AIB協定的科技積累,提出了跨公司、跨工藝互聯的UCIe協定。

從上圖可以看出,英特爾的AIB協定主要應用在軍工和航空航太產品上。 而基於AIB經驗積累開發的UCIe協定,在速率、協定層的支持以及封裝技術上都具有明顯的優勢。 相比之下,類似HBI、BOW等協定自UCIe協定問世以來,更新頻率逐漸降低,其規範的內容細緻程度也遠不及UCIe協定。

中國全自主可控的Chiplet高速串口標準ACC 1.0於2023年3月20日發佈。 隨後,中國Chiplet產業聯盟發佈了ACC_RV 1.0車規級芯粒互聯介面標準,為中國Chiplet互聯科技的發展起到了關鍵的推動作用。

UCIe協定構成

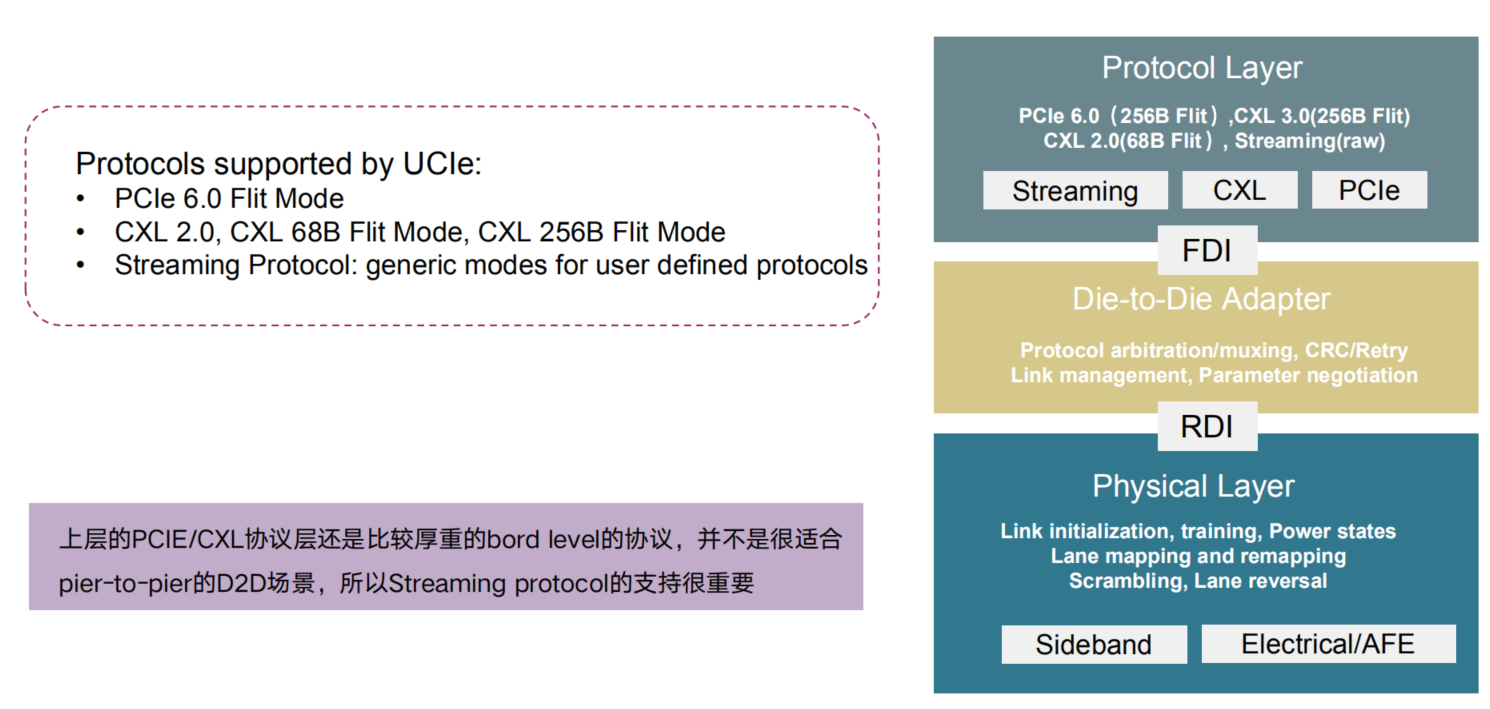

UCIe協定包含三個層級,分別是協議層(Protocol Layer)、適配層(Die-to-Die Adapter Layer)以及實體層(Physical Layer)。 這三個層級在協定的整體結構中擔任不同的角色,具體如下:

協定層(Protocol Layer):

UCIe支持的協定包括PCI Express、CXL和Streaming。

採用基於Flit的協定,以提供最高效率和减少延遲。

裸晶互連連接層(Die-to-Die Adapter Layer):

負責連結管理功能,包括協定仲裁和協商。

提供基於CRC和Retry的可選糾錯功能。

實體層(Physical Layer):

包含Electrical/AFE和邏輯PHY,用於實現連結初始化、訓練和校準算法,以及測試和修復功能。

邊帶(Sideband)用於實現兩個晶片之間的參數交換和協商。

在協定層到裸晶互連連接層的介面被稱為FDI(Flit Data Interface),而裸晶互連連接層到實體層的介面則稱為RDI(Raw Data Interface)。 在FDI的邊界上,它具備同時支持多個協定層掛載的能力。 在不同的應用場景下,可以選擇使用不同的協定,而由裸晶互連連接層負責進行仲裁。 這種應用在未來CXL中將變得非常重要。 因為CXL本身涵蓋三種協定:.io、.memory、.cache。 這種設計允許在接入UCIe時實現無縫銜接,並直接通過一個通路傳輸。 而在RDI的邊界上,可以連接單一模塊的PHY,也可以連接多個模塊的PHY,這種配寘非常靈活。 囙此,總體上說,整個多層邊界的定義非常清晰。

現時,UCIe支持的都是Flit模式的傳輸(即固定包層的傳輸)。 傳輸包的大小可能是68位元組的Flit,或是256位元組的Flit,這取決於所採用的協定。 例如,PCIe 6.0和CXL 3.0都採用256位元組的Flit,而對於CXL 2.0,則需要轉換成68位元組的Flit模式進行傳輸。 Streaming模式是相容其他協定的一種模式,其要求是採用64位元組的原始模式。 其他協定或PCIe、CXL的其他版本可能需要進行轉換,以適應這種原始模式進行傳輸。

作為UCIe產業聯盟和中國電腦互連科技聯盟(CCITA)的成員,奎芯科技致力於推動芯粒互聯科技的發展和應用。 在高速介面IP領域,奎芯科技擁有深厚的科技積累和豐富的產品系列。 基於這些高端的高速介面IP,奎芯科技提出了一種名為M2LINK的計算機系統互聯架構方案。

M2LINK包含三種Chiplet方案:C2IO,與串列匯流排介面相聯; C2M,與記憶體匯流排相連; 以及C2C,實現計算Die之間的互聯。 奎芯科技將不斷努力以滿足Chiplet領域晶片設計企業的需求,並致力於打造一個開放生態的Chiplet服務平臺,為集成晶片和芯粒行業的創新和發展提供全方位的支持。