前言

在前文《片內封裝級互聯—奎芯Chiplet D2D接口技術》中有提及Chiplet其實不是新技術了,FPGA很早的時候就採用Chiplet科技,甚至用了3D的封裝,但是這些產品的出貨量比較小,也不具備典型性,直到15,16年AMD ZEN系列處理器出來後,這個科技才被廣泛的傳播開來。 所以小編今天想從AMD霄龍處理器對外發佈的一些公開資訊中,通過分析AMD霄龍處理器內部Chiplet結構的演變,來看看能有什麼新發現。

Zen是AMD開發的全新x86處理器核心,是一種微處理器架構,採用Zen微架構的處理器名氣最大當屬霄龍(針對服務器的平臺)和銳龍(針對桌面的平臺),而從霄龍二代和銳龍三代開始,AMD採用就采用CPU die + IO die的Chiplet組合管道來擴展CPU算力,其中CPU die簡稱CCD(Zen架構將以四個覈心為一個群組,AMD將其稱為“CPU Complex”(CCX),也就是“CPU複合體”的意思,每兩個CCX組合成一個CCD),IO die簡稱IOD。

可以看到霄龍3代和2代的核心參數改變不大,3代CCD和2代的CCD都是採用T7nm的工藝,但是從Zen2架構到Zen3架構的改變還是蠻大的,比如AMD將原來Zen2 CCX中三級緩存16MB+16MB折開設計改成1個32MB+,以降低內核對三級緩存的訪問延遲。 3代霄龍的IOD從2代採用的GF14nm工藝升級到12nm工藝,GF12/14nm應該是一個節點,12nm是14nm的改良版,能够獲得更緊湊的面積和更低的功耗,IOD的結構和功能並沒有明顯的改變。

霄龍4代相比3代提升還是很明顯的,首先支持最大覈心數從64核提升到96核,也就是單IOD最多可支持12個CCD的組合,一共有13個Chiplet小晶片構成。 CCD也從台積電的7nm升級到5nm,IOD的升級尤為明顯,由於GF不再涉足7nm Finfet及更先進的工藝,IOD也採用了台積電的6nm工藝,片上記憶體,PCIe等介面都獲得了極大提升。

圖3:霄龍二代IOD的內部照

圖4:霄龍二代IOD的功能框圖

圖3是一個二代霄龍IOD的內部照,IOD擁有83.4億個電晶體、416平方毫米,左右兩側紫色的是分成八組的雙通道DDR4的PHY,總位寬576-bit,最高頻率3200Mhz,緊靠著DDR PHY的標注MC的是DDR控制器; 中間上下紅色的是支持PCIe Gen4的SerDes PHY,總計128條; 在旁邊紫色標注CCD IFOP PHY的部分則是GMI2介面的PHY,通過AMD Infinity Fabric科技連接CCD和IOD,可以理解為AMD的D2D的介面。

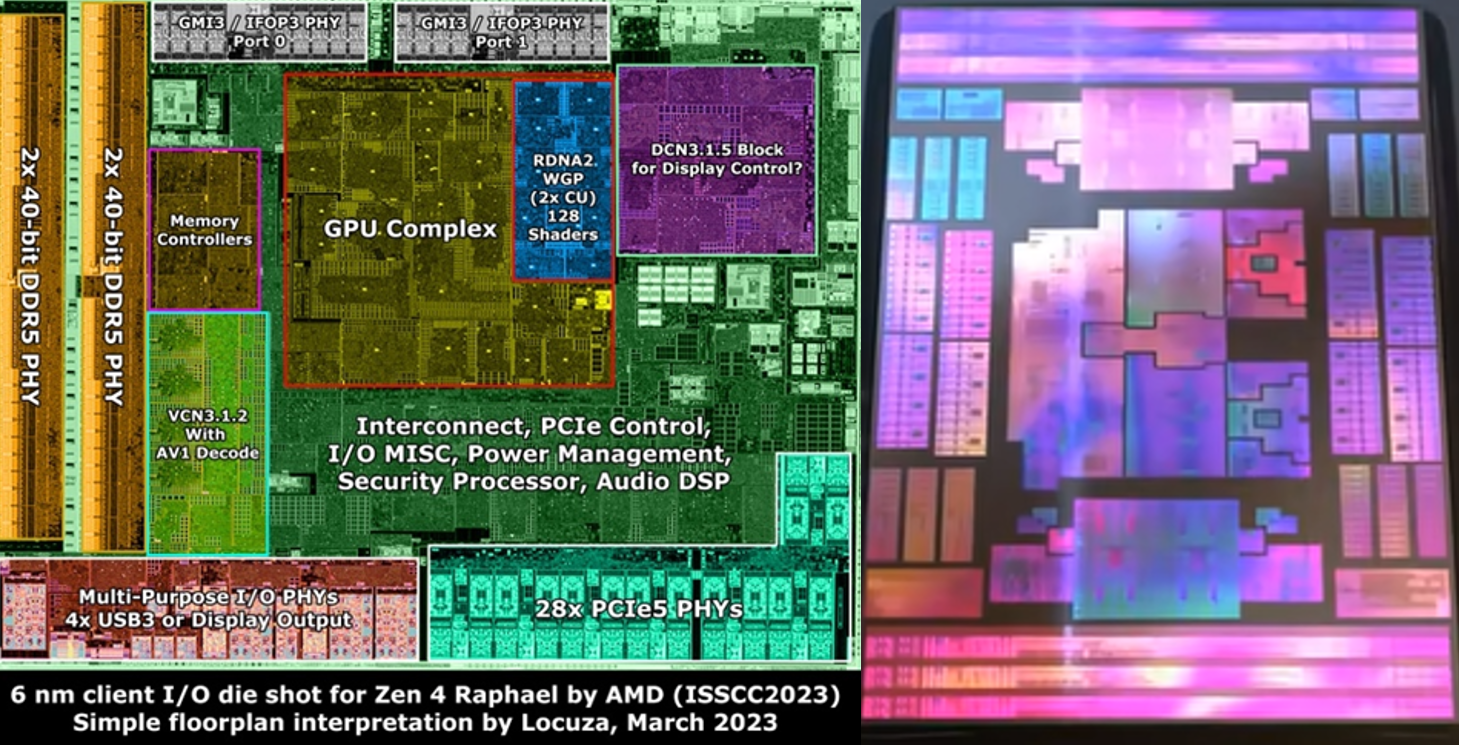

圖5:Zen 4架構下霄龍4代和銳龍7000系列的IOD

IEEE ISSCC 2023國際固態電路大會上,AMD披露了部分霄龍4代IOD的資訊,可以看到台積電6nm工藝下霄龍4代IOD的面積僅為24.8×15.6=386.88平方毫米,多支持4個CCD的情况下面積依舊小於2代的IOD,總計約110億個電晶體,電晶體密度提升顯著。 同時這邊還披露了銳龍7000系列的IOD,也是基於6nm工藝,但是桌面應用中的核心顯卡整合在IOD中,所以結構上不能簡單的認為是霄龍4代IOD的簡化版。

圖6:銳龍IOD的詳細佈局圖+霄龍4代IOD的渲染圖

現時由於未能找到霄龍4代IOD的實圖,輔以圖6右側AMD渲染美圖替代,圖6左側是銳龍IOD的詳細佈局圖,我們借其標注的一些介面來看看4代霄龍IOD有哪些提升。

記憶體介面方面,霄龍4代擁有12通道DDR5-4800,從通道個數上比上一代多50%,AMD還將從DDR4-3200速度提高到DDR5-4800速度,從而大幅提升每通道頻寬。

霄龍4代利用出色的SerDes效能,每個處理器依舊是128通道,64(或4×16)支持xGMI(插槽到插座Infinity Fabric)和PCIe Gen5(霄龍二代和三代是PCIe Gen4)。 其他64個通道支持xGMI,PCIe,CXL和SATA。 另外還有一些額外的PCIe3.0*8的通道,支持SATA低速傳輸,霄龍2代和3代中則有有4個。

GMI介面也從GMI2升級到GMI3了,第四代EPYC(霄龍)CPU可將8核CCD的數量從4個擴展到12個,4* CCD變體(最多32個內核)有一個有趣的技巧,它們可以為每個CCD獲得2倍的IO晶片連結,也就是單CCD可以通過兩個GMI3連結連接到IOD,而12和8 CCD變體只有一個GMI3連結連接到IO晶片。

AMD採用Chiplet科技打造CPU的策略所引發的市場關注和業績來看,已經形成了的正向的迴響。 IOD可以選擇最適合的工藝節點,不用緊跟CPU core採用最先進的工藝節點,可以每兩三代處理器更新的時候再做一次大的反覆運算,性價比簡直拉滿。 從二代霄龍的IOD可以看到佔據晶片面積最大的部分是各類高速介面的PHY,其次是它們的控制器電路,在數據大爆發的時代,高性能計算離不開高速介面IP的支持,從高速介面IP佔據IOD晶片面積的比例,其重要性已不言而喻。 奎芯科技在DDR類和SerDes類介面均有佈局,已陸續研發推出LPDDR、HBM、PCIe、SerDes、MIPI、USB、ONFI等IP和解決方案,針對大算力晶片Chiplet應用,奎芯科技可以提供M2LINK-D2D的方案,採用DDR架構,支持UCIe和Chiplet互聯標準。